### Beyond the Bandwidth Wall: Unlocking Hardware Freedom and Performance with Al Ramp Accelerate

A Strategic Overview for Al Infrastructure Leaders

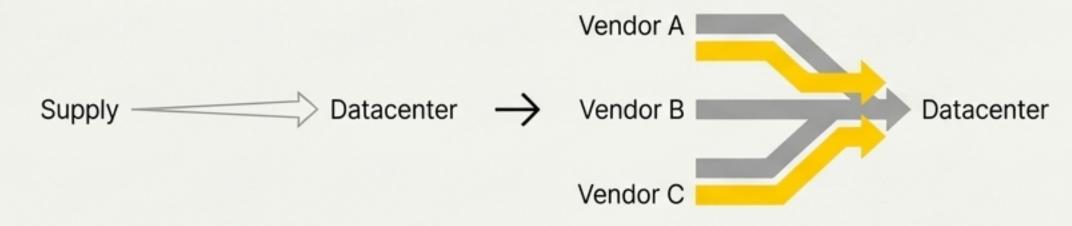

#### The Al Arms Race Has Created a Hardware Monopoly, Trapping You in a Cycle of Scarcity, Cost, and Risk.

Your ability to scale is dictated by a single vendor's roadmap and supply chain, not your own strategic plan.

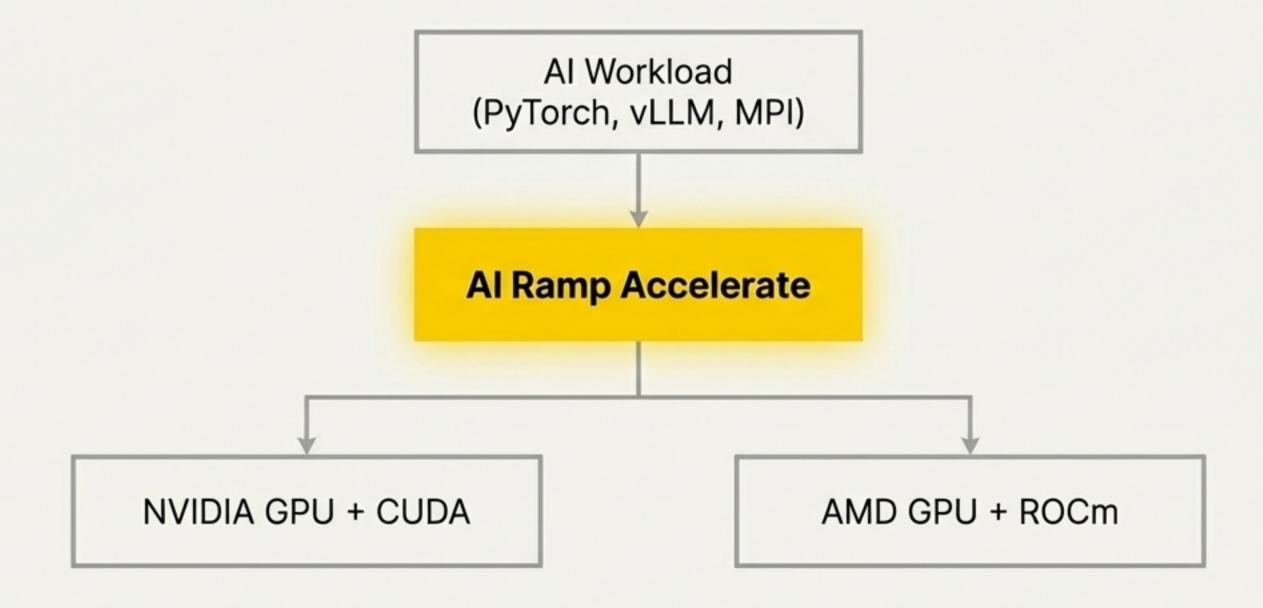

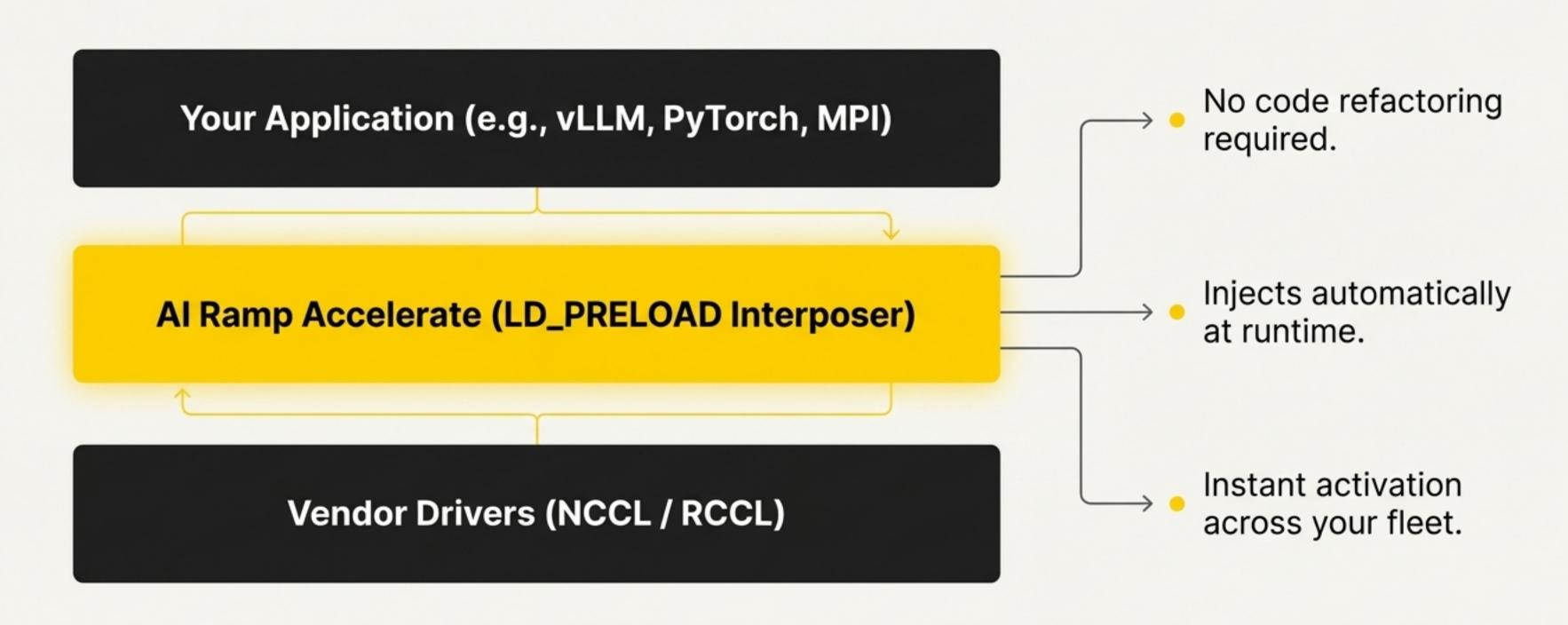

### Al Ramp Accelerate is a Zero-Code Software Layer that Unlocks a Multi-Vendor, High-Performance Compute Fabric.

We break the hardware dependency by abstracting and optimizing the communication layer. You can now deploy the best silicon for the job, without refactoring your software.

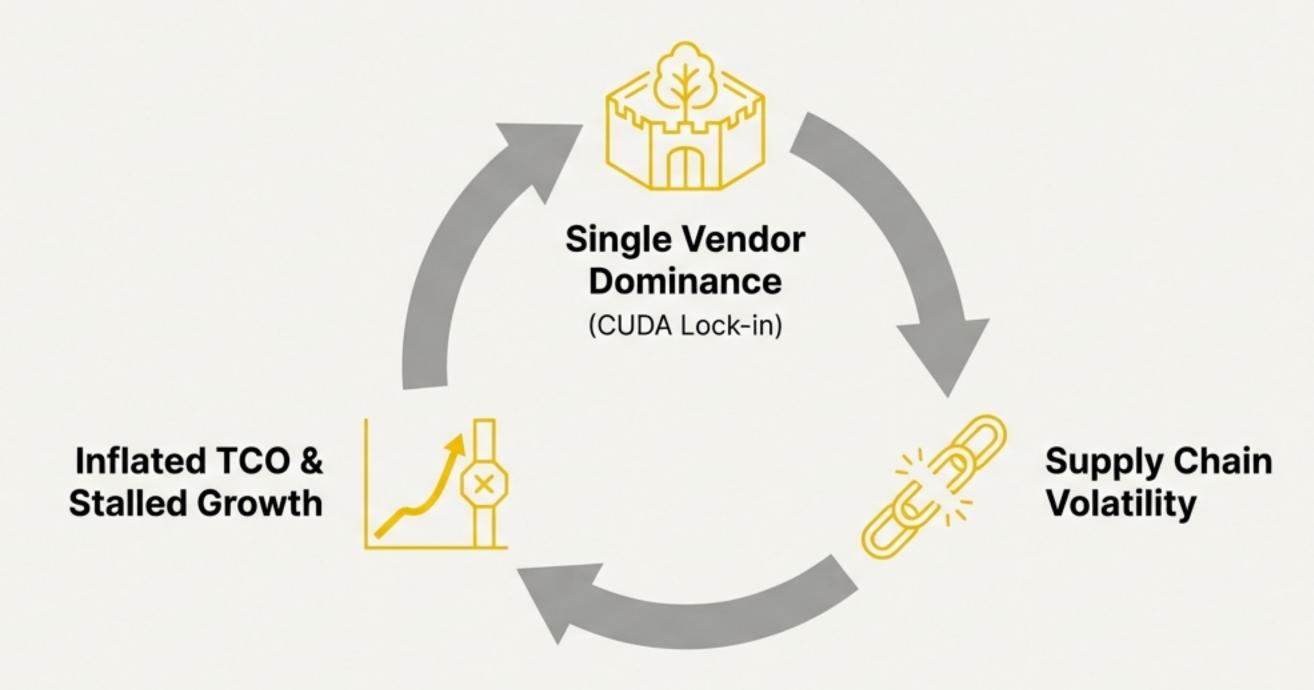

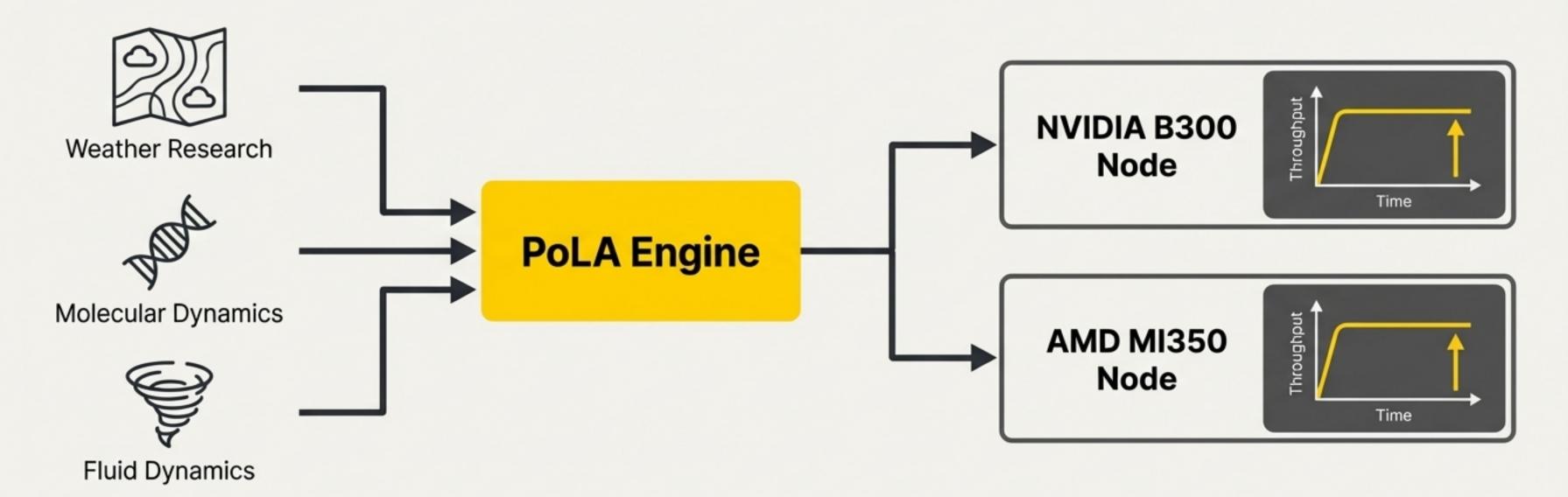

## We Operate as a Transparent Shim Layer, Injecting Optimizations Without a Single Code Change.

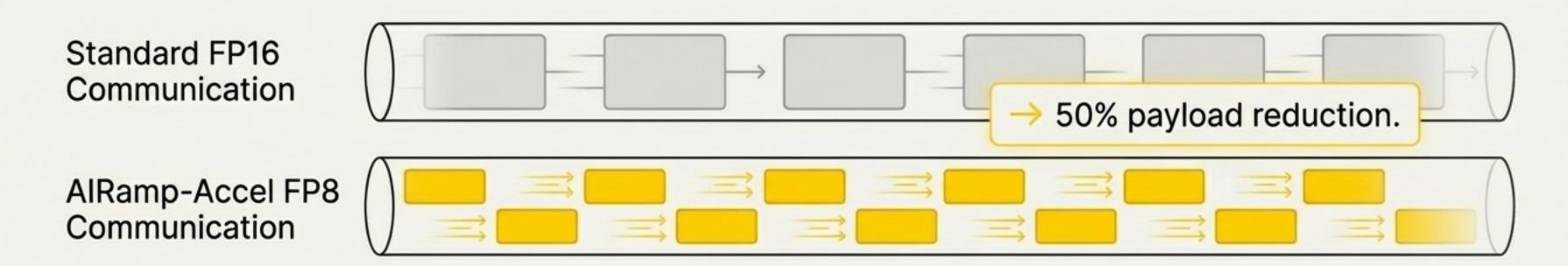

### The First Engine: Doubling Bandwidth with FP8 "Zero-Sync" Compression.

For bandwidth-heavy Tensor Parallel operations (e.g., AllReduce), we intercept FP16 calls and compress them to FP8 on-the-fly.

This doubles the effective bandwidth of your interconnect (NVLink, Infinity Fabric).

For massive 70B+ models, this turns a communication bottleneck into a compute opportunity, directly increasing Token-Per-Second throughput.

Safety check: Compression is only applied to large tensors (default >1MB) to leave sensitive metadata intact.

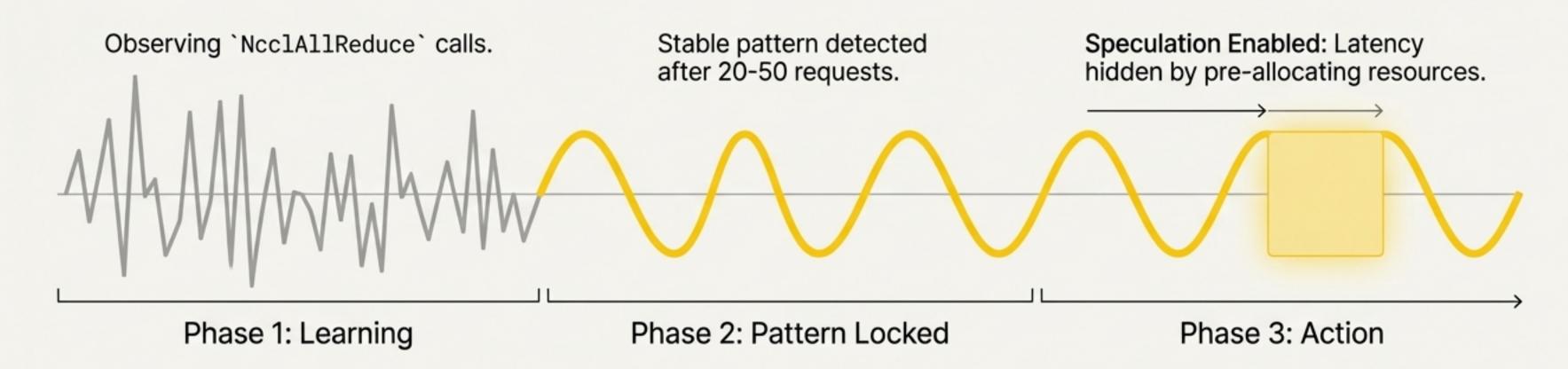

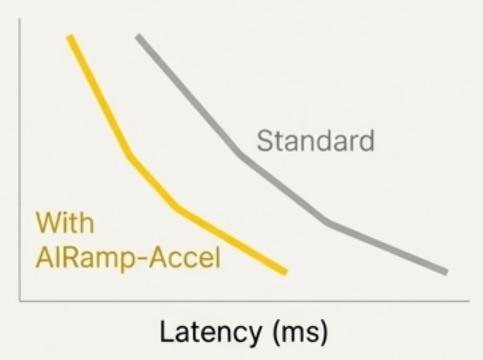

### The Second Engine: Predicting Workload Rhythms with Pattern-of-Life Analysis (PoLA).

Our predictive engine observes the size and frequency of communication calls in repetitive workloads like LLM inference and HPC simulations.

Once a pattern is locked, we **pre-allocate buffers** and pre-**configure** communication **rings** before the application requests them.

This proactive orchestration effectively hides CPU and initialization latency, maximizing GPU uptime.

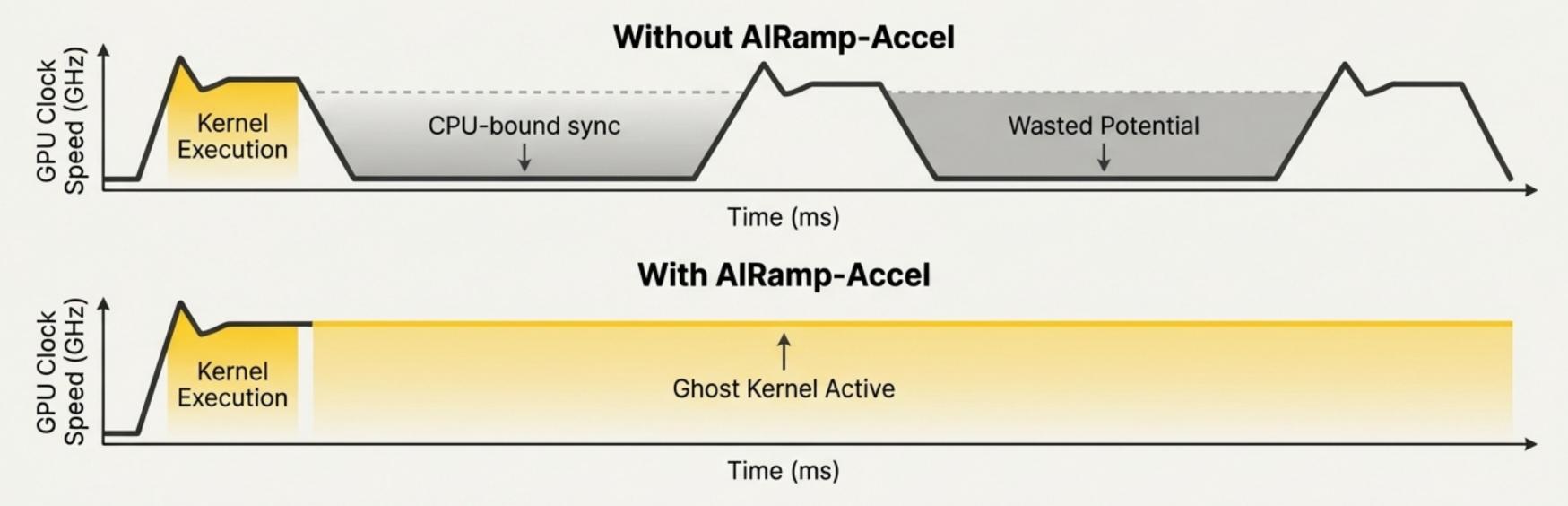

## The Third Engine: Eliminating Idle Time with Lightweight "Ghost Kernels".

- CPU-to-GPU launch latency can cause micro-stalls, leaving GPUs idle and prone to downclocking.

- We launch lightweight "Ghost Kernels" to keep the command queues active and clock speeds boosted during these intervals.

- This turns microseconds of idle time—magnified across a large cluster—into sustained peak performance and maximum FLOP utilization.

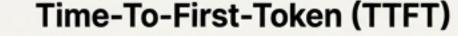

# For Llama 3 70B on 8x GPUs, AlRamp-Accel Directly Boosts Token-Per-Second Throughput.

### **Tokens-Per-Second Gain in Generation Phase**

**Generation Phase (Decode):** This memory-bandwidth bound phase sees the most significant TPS lift from FP8 compression's 50% data payload reduction.

**Prompt Phase (Pre-fill):** Faster interconnect clearing provides a slight reduction in TTFT.

Simple Activation: This performance is unlocked with a single flag: AIRAMP\_ENABLE\_FP8\_ALLREDUCE=1

# We Optimize the Cyclical Nature of HPC Simulations Across Heterogeneous Hardware.

The same 'Pattern-of-Life' analysis that benefits LLMs detects the rigid periodicity of HPC time-steps. **Our single software layer unifies your AI and HPC stacks**, allowing you to **run any workload on any hardware without code refactoring.**

## Uptime is Paramount. AlRamp-Accel is Designed to Be Invisible or Evaporate, Never to Fail.

In any error state (mismatched driver, OOM, config error), the application does not crash. It simply continues to run at standard speed. Optimization is an enhancement, not a dependency.

# Every Stage of Operation is Guarded by Safety Checks to Ensure Stability.

#### **Initialization Safety**

Gracefully enters a passthrough "inert" state if vendor drivers (e.g., `libcudart.so`) are missing or incompatible. It logs a warning, but never crashes the application.

#### **Kernel Loading Safety**

Verifies hardware-specific binaries (CUBINs/HSACOs) are valid for the detected GPU architecture before loading. This prevents "illegal instruction" faults in mixed-hardware clusters.

#### **Runtime Safety**

Handles Out-Of-Memory (OOM) errors and consensus timeouts by reverting to the standard communication path. This prevents application hangs and memory faults.

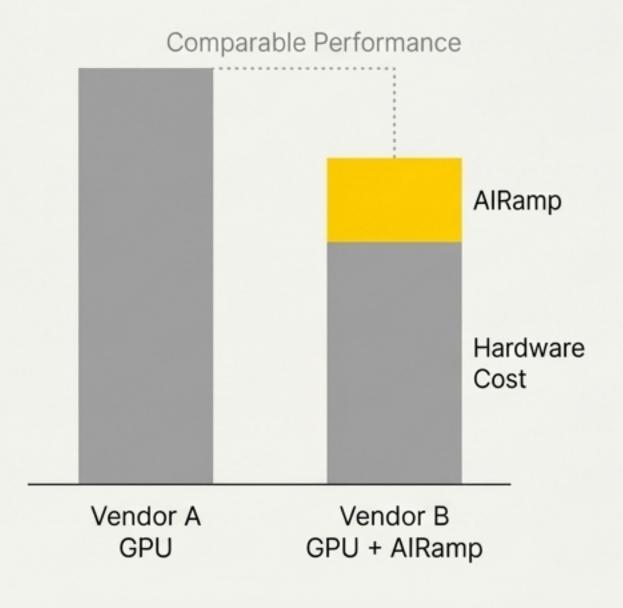

### AlRamp-Accel Fundamentally Reshapes Data Center TCO and ROI

#### 1. Drastically Lower TCO

#### 2. Mitigate Supply Chain Risk

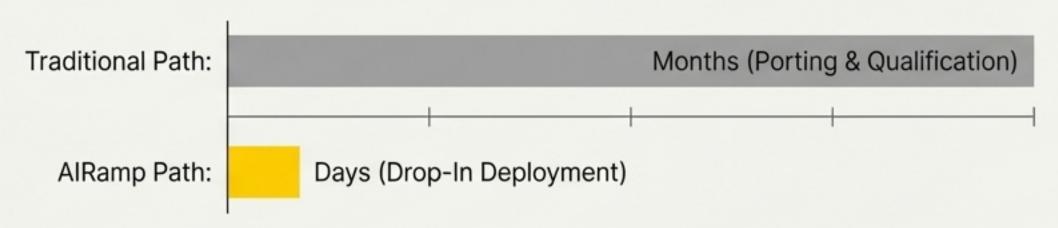

#### 3. Accelerate Time-to-Market

# Al Ramp Accelerate is More Than an Optimizer—It's Your Path to an Open, Efficient, and Resilient Al Future.

#### Unlock Unlock Hardware Freedom

Break the CUDA lock-in.

Deploy the best available silicon from any vendor.

Mitigate supply chain risk.

#### Maximize Infrastructure Performance

Extract maximum value from every GPU with autonomous, zero-code optimizations like FP8 compression and PoLA.

# Deploy with Absolute Confidence

Our 'Fail-Soft' architecture ensures zero operational risk to your mission-critical workloads.

## Let's Define Your Path to a More Efficient Infrastructure.

- Request a Technical Deep Dive with Our Engineers

- Schedule a Proof-of-Concept on Your Workloads

- Contact Us: accelerate@tensor-networks.com | www.tensor-networks.com

### Thank You

Q&A